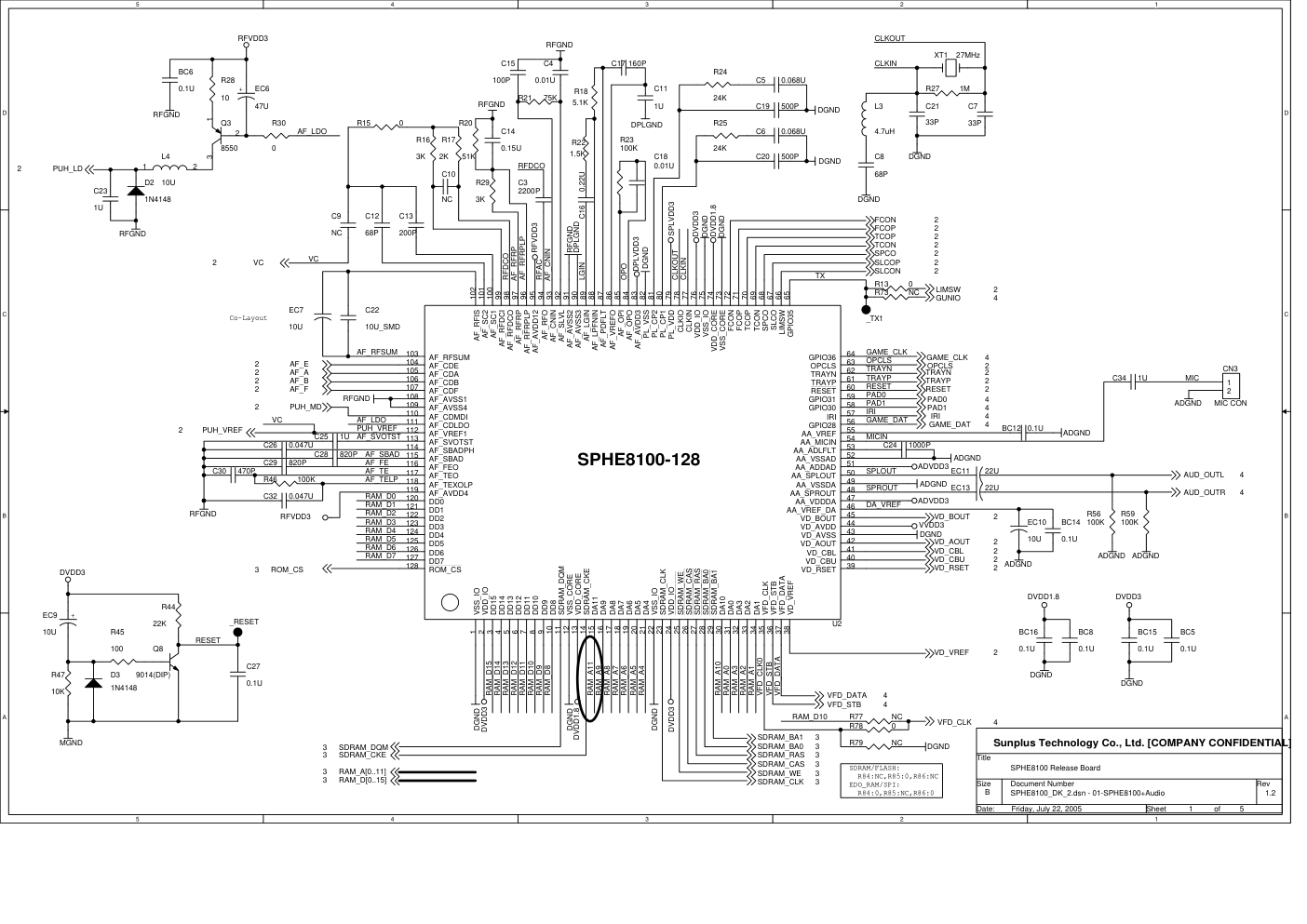

采用SPHE8100芯片的DVD机电路原理图

)

)

)

)

)

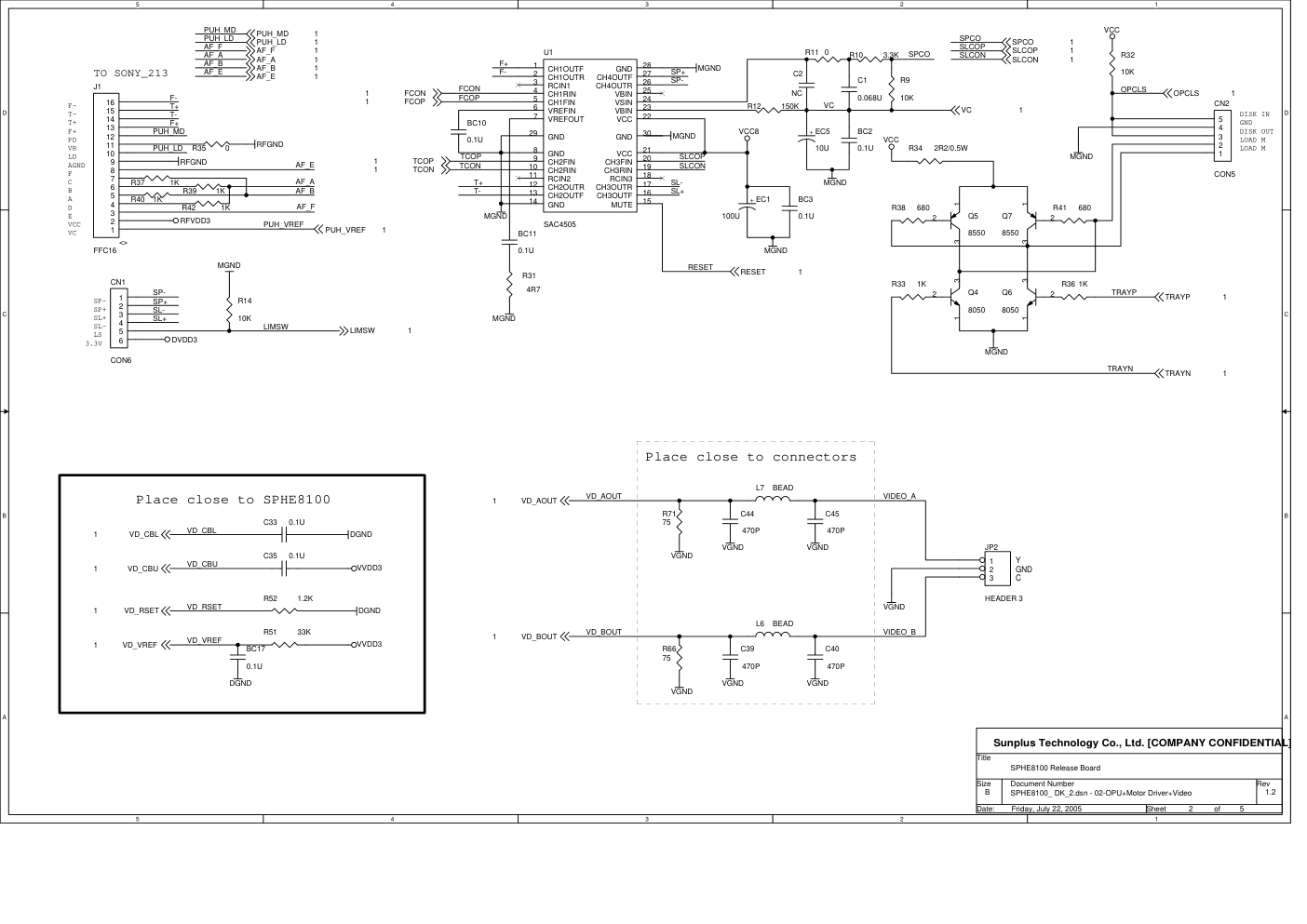

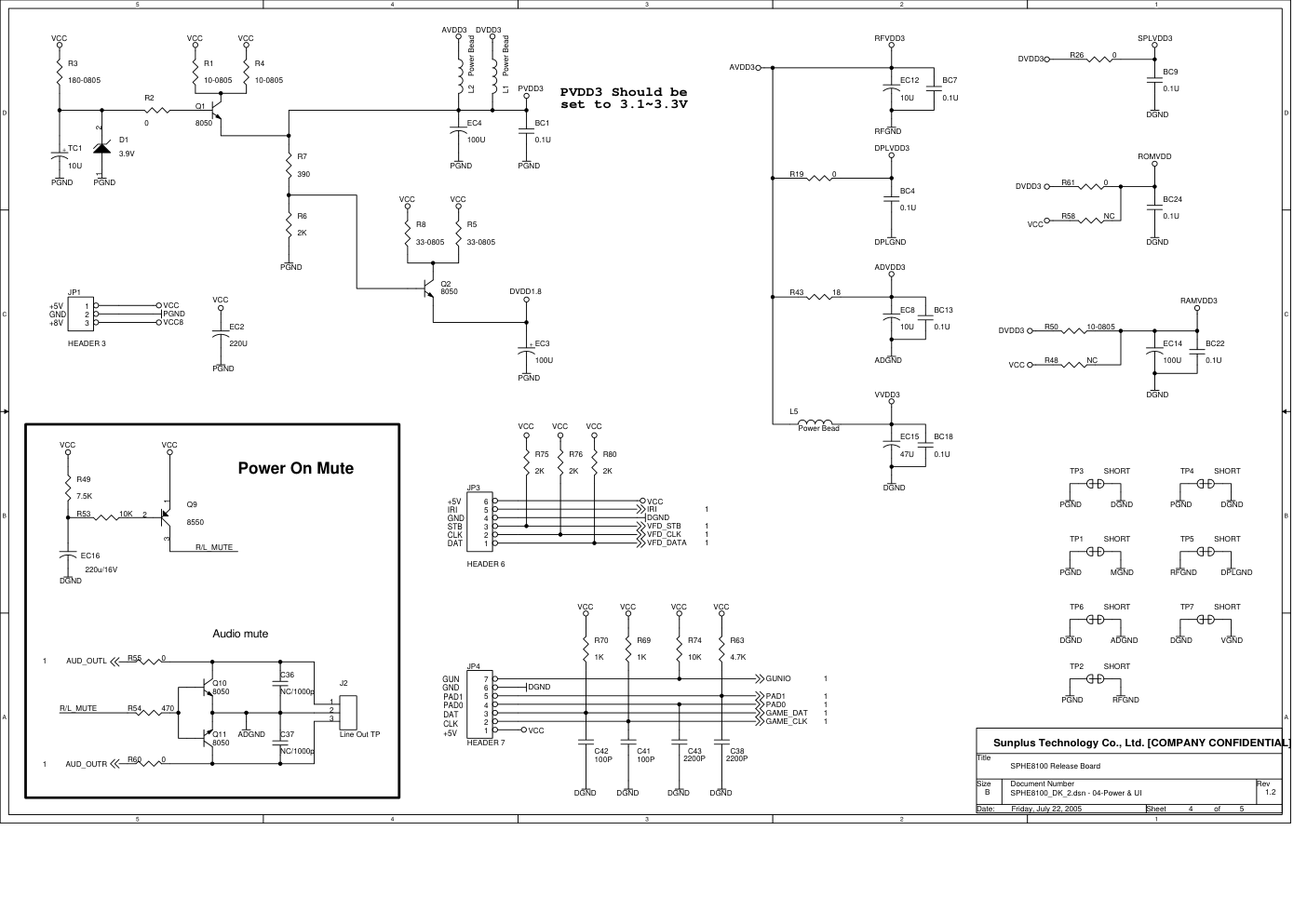

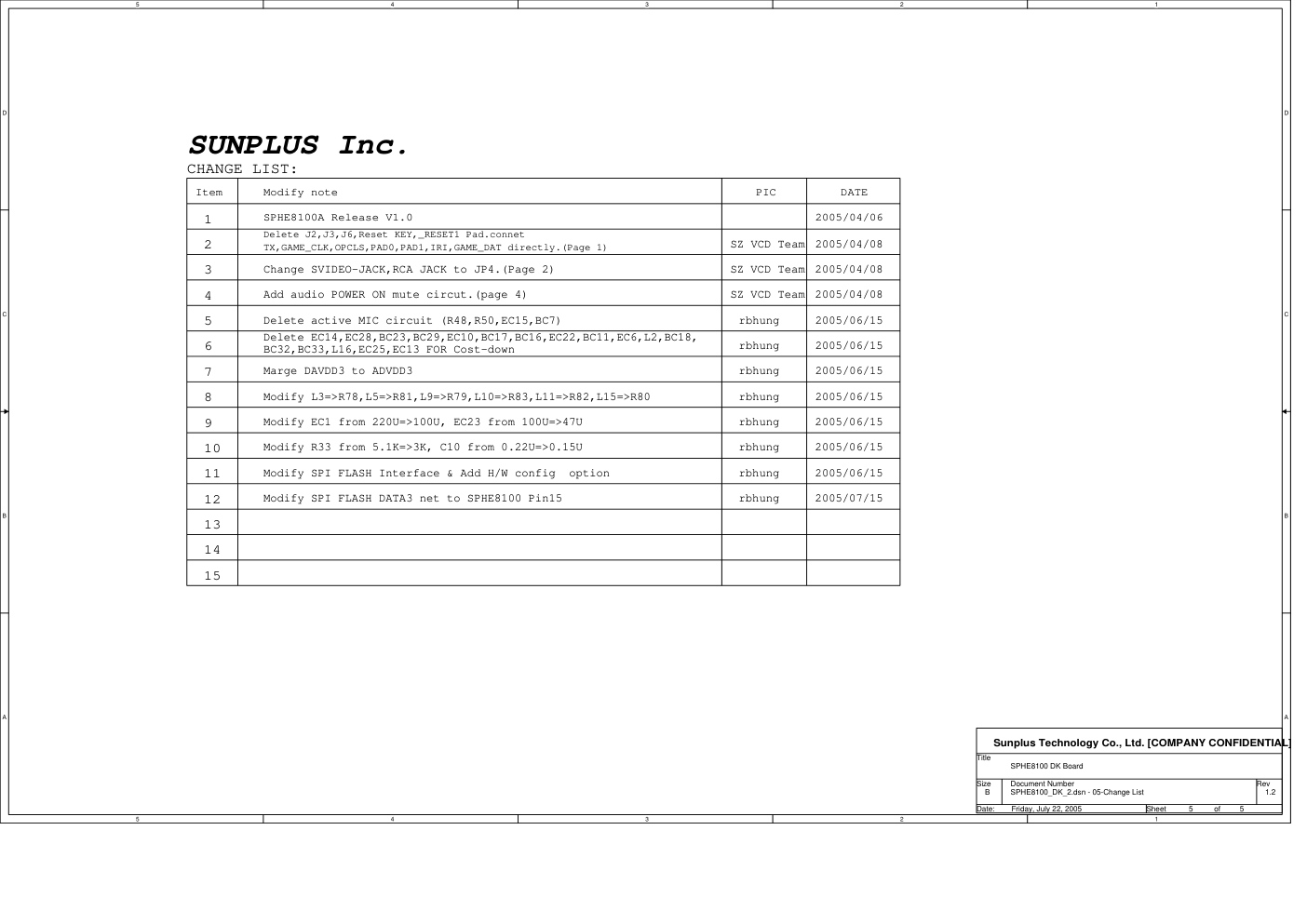

5 4 3 2 1 D D C C B B A A SDRAM/FLASH: EDO_RAM/SPI: R84:NC,R85:0,R86:NC R84:0,R85:NC,R86:0 Co-Layout SPHE8100_DK_2.dsn - 01-SPHE8100+Audio 1.2 SPHE8100 Release Board Sunplus Technology Co., Ltd. [COMPANY CONFIDENTIAL] B 1 5 Friday, July 22, 2005 Title Size Document Number Rev Date: Sheet of AF_LDO RAM_D5 RAM_D7 PAD1 GAME_DAT RAM_D11 TRAYP RFDCO AF_RFRP AF_RFRPLP RAM_D4 RAM_D6 RAM_A3 OPO CLKIN AF_FE RAM_D13 RAM_D10 RAM_D8 VFD_DATA AF_TELP SPLOUT RAM_A10 RAM_A7 VC LGIN PAD0 VFD_CLK0 RAM_A5 VC RFDCO AF_CNIN AF_RFSUM PUH_VREF RESET IRI RAM_A0 RAM_A1 RAM_D3 RAM_D14 RAM_A8 AF_SBAD VFD_STB RAM_A9 CLKOUT RFAC RAM_D0 RAM_D2 SPROUT RAM_A2 RAM_A6 RAM_D1 RAM_D15 AF_SVOTST RAM_D12 RAM_D9 RAM_A4 AF_TE CLKOUT CLKIN OPCLS GAME_CLK TRAYN MICIN DA_VREF MIC AF_LDO TX RESET RAM_D10 RAM_A11 PUH_MD 2 RAM_A[0..11] 3 VC 2 VFD_DATA 4 VFD_STB 4 VFD_CLK 4 RAM_D[0..15] 3 SDRAM_BA1 3 SDRAM_BA0 3 SDRAM_CAS 3 SDRAM_WE 3 SDRAM_CLK 3 SDRAM_DQM 3 SDRAM_CKE 3 SDRAM_RAS 3 AF_A 2 AF_E 2 AF_B 2 AF_F 2 ROM_CS 3 PUH_VREF 2 FCON 2 FCOP 2 TCOP 2 TCON 2 SPCO 2 SLCOP 2 SLCON 2 VD_AOUT 2 VD_CBL 2 VD_CBU 2 VD_RSET 2 VD_VREF 2 VD_BOUT 2 TRAYN 2 TRAYP 2 RESET 2 PUH_LD 2 GUNIO 4 LIMSW 2 IRI 4 GAME_CLK 4 OPCLS 2 PAD0 4 PAD1 4 GAME_DAT 4 AUD_OUTR 4 AUD_OUTL 4 DVDD1.8 DGND DPLGND MGND DVDD3 DGND RFGND RFVDD3 DGND DGND RFGND DVDD3 DGND DVDD3 DPLGND RFGND DGND DVDD1.8 DPLVDD3 SPLVDD3 DVDD3 RFVDD3 ADGND RFGND DGND DGND DGND ADVDD3 DVDD3 DGND DGND DVDD1.8 ADGND ADGND VVDD3 DGND DGND RFGND RFGND RFGND RFVDD3 ADGND ADVDD3 ADGND ADGND ADGND DGND EC7 10U R44 22K C20 500P R25 24K BC8 0.1U + EC6 47U BC15 0.1U C7 33P C14 0.15U C19 500P R29 3K C27 0.1U C29 820P R27 1M C30 470P R28 10 C10 NC U2 SPHE8100-128 102 101 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 64 63 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 1 2 3 4 5 6 7 8 9 10 11 13 15 12 14 25 26 27 28 29 30 31 32 33 34 35 36 37 38 16 17 18 19 20 21 22 23 24 65 78 77 76 75 74 73 72 71 70 69 68 67 66 62 AF_RFIS AF_SC2 AF_SC1 AF_RFDCI AF_RFDCO AF_RFRP AF_RFRPLP AF_AVDD12 AF_RFO AF_CNIN AF_SLVL AF_AVSS2 AF_AVSS3 AF_LGIN AF_LPFNIN AF_PDFLT AF_VREFO AF_OPI AF_OPO AF_AVDD3 PL_VSS PL_CP2 PL_CP1 PL_VDD AF_RFSUM AF_CDE AF_CDA AF_CDB AF_CDF AF_AVSS1 AF_AVSS4 AF_CDMDI AF_CDLDO AF_VREF1 AF_SVOTST AF_SBADPH AF_SBAD AF_FEO AF_TEO AF_TEXOLP AF_AVDD4 DD0 DD1 DD2 DD3 DD4 DD5 DD6 DD7 ROM_CS GPIO36 OPCLS TRAYP RESET GPIO31 GPIO30 IRI GPIO28 AA_VREF AA_MICIN AA_ADLFLT AA_VSSAD AA_ADDAD AA_SPLOUT AA_VSSDA AA_SPROUT AA_VDDDA AA_VREF_DA VD_BOUT VD_AVDD VD_AVSS VD_AOUT VD_CBL VD_CBU VD_RSET VSS_IO VDD_IO DD15 DD14 DD13 DD12 DD11 DD10 DD9 DD8 SDRAM_DQM VDD_CORE DA11 VSS_CORE SDRAM_CKE SDRAM_WE SDRAM_CAS SDRAM_RAS SDRAM_BA0 SDRAM_BA1 DA10 DA0 DA3 DA2 DA1 VFD_CLK VFD_STB VFD_DATA VD_VREF DA9 DA8 DA7 DA6 DA5 DA4 VSS_IO SDRAM_CLK VDD_IO GPIO35 CLKIO CLKIN VDD_IO VSS_IO VDD_CORE VSS_CORE FCON FCOP TCOP TCON SPCO SLCO LIMSW TRAYN BC14 0.1U C21 33P R77 NC D3 1N4148 BC12 0.1U C16 0.22U BC5 0.1U C11 1U Q3 8550 2 1 3 CN3 MIC CON 1 2 R46 100K R17 2K R21 75K XT1 27MHz R56 100K R78 0 C9 NC Q8 9014(DIP) C18 0.01U + EC9 10U L4 10U 1 2 C12 68P EC11 22U D2 1N4148 C32 0.047U _RESET R59 100K BC6 0.1U R22 1.5K EC10 10U C34 1U R23 100K C24 1000P R16 3K C22 10U_SMD R79 NC R47 10K R20 51K _TX1 C25 1U EC13 22U C23 1U R15 0 R30 0 C13 200P L3 4.7uH C6 0.068U BC16 0.1U C8 68P R45 100 R24 24K C26 0.047U C15 100P C5 0.068U R18 5.1K R13 0 R73 NC C3 2200P C4 0.01U C17 160P C28 820P 5 4 3 2 1 D D C C B B A A 3.3V SL- LS SP- SP+ SL+ F- T- T+ F+ LD AGND F C B A D E VCC VC VR PD TO SONY_213 DISK IN GND DISK OUT LOAD M LOAD M Place close to connectors Place close to SPHE8100 GND C Y SPHE8100_ DK_2.dsn - 02-OPU+Motor Driver+Video 1.2 SPHE8100 Release Board Sunplus Technology Co., Ltd. [COMPANY CONFIDENTIAL] B 2 5 Friday, July 22, 2005 Title Size Document Number Rev Date: Sheet of SL- SP- SP+ SL+ AF_F T+ T- F+ F- PUH_VREF PUH_LD PUH_MD TRAYP TRAYN VIDEO_A VD_AOUT VD_RSET VD_CBL VIDEO_B VD_BOUT VD_VREF PUH_MD PUH_LD AF_F AF_A AF_B AF_E OPCLS SLCOP SPCO F- SL- SP- SP+ F+ RESET SL+ AF_E SLCON SLCOP SLCON TCOP TCON T- T+ AF_A AF_B FCON FCOP LIMSW VC SPCO VD_CBU VD_CBL 1 VD_RSET 1 VD_VREF 1 VD_AOUT 1 VD_BOUT 1 TRAYP 1 TRAYN 1 OPCLS 1 PUH_VREF 1 SPCO 1 AF_F 1 AF_A 1 AF_B 1 PUH_MD 1 PUH_LD 1 AF_E 1 RESET 1 SLCOP 1 SLCON 1 FCON 1 FCOP 1 TCOP 1 TCON 1 LIMSW 1 VC 1 VD_CBU 1 RFVDD3 RFGND DVDD3 RFGND VCC VCC VGND VGND VGND VVDD3 DGND DGND VGND VGND VGND DGND MGND MGND VCC8 MGND MGND MGND MGND MGND VVDD3 VGND MGND MGND R9 10K R37 1K C45 470P R35 0 Q4 8050 2 1 3 R32 10K C39 470P BC10 0.1U BC2 0.1U R51 33K U1 SAC4505 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 CH1OUTF CH1OUTR RCIN1 CH1RIN CH1FIN VREFIN VREFOUT GND CH2FIN CH2RIN RCIN2 CH2OUTR CH2OUTF GND MUTE CH3OUTF CH3OUTR RCIN3 CH3RIN CH3FIN VCC VCC VBIN VSIN VBIN CH4OUTR CH4OUTF GND GND GND C40 470P R52 1.2K R36 1K BC11 0.1U J1 <> FFC16 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 R14 10K L6 BEAD BC17 0.1U C35 0.1U R11 0 R33 1K R39 1K R31 4R7 R71 75 C33 0.1U C2 NC JP2 HEADER 3 1 2 3 R40 1K Q7 8550 2 1 3 CN1 CON6 1 2 3 4 5 6 R38 680 BC3 0.1U L7 BEAD R66 75 + EC1 100U Q5 8550 2 1 3 R42 1K CN2 CON5 1 2 3 4 5 R12 150K R34 2R2/0.5W R10 3.3K C1 0.068U Q6 8050 2 1 3 R41 680 C44 470P + EC5 10U 5 4 3 2 1 D D C C B B A A RAM Bus: 1-2 ROM 2-3 FLASH ROM Bus: 1-2 ROM 2-3 FLASH Shared/SPI-1/EDO SPHE8100_DK_2.dsn - 03-Memory 1.2 SPHE8100 Release Board Sunplus Technology Co., Ltd. [COMPANY CONFIDENTIAL] B 3 5 Friday, July 22, 2005 Title Size Document Number Rev Date: Sheet of RAMX_A10 RAM_A10 RAMX_A8 RAM_A8 RAMX_A9 RAM_A9 RAMX_A3 RAM_A3 RAMX_A5 RAM_A5 RAMX_A7 RAM_A7 RAMX_A4 RAM_A4 RAMX_CAS SDRAM_CAS RAMX_WE SDRAM_WE RAMX_A0 RAM_A0 SDRAMX_DQM0 SDRAM_DQM RAMX_A2 RAM_A2 RAMX_A1 RAM_A1 SDRAMX_CLK RAM_CLK RAMX_RAS0 SDRAM_RAS SDRAMX_BA0 SDRAM_BA0 SDRAMX_CKE SDRAM_CKE RAMX_D15 RAM_D15 RAMX_D14 RAM_D14 RAMX_D13 RAM_D13 RAMX_D12 RAM_D12 RAMX_D11 RAM_D11 RAMX_D7 RAM_D7 RAMX_D8 RAM_D8 RAMX_D9 RAM_D9 RAMX_D10 RAM_D10 RAMX_D6 RAM_D6 RAMX_D3 RAM_D3 RAMX_D2 RAM_D2 RAMX_D4 RAM_D4 RAMX_D5 RAM_D5 RAMX_D1 RAM_D1 RAMX_D0 RAM_D0 ROMX_A12 RAM_A9 ROMX_WE RAM_A4 ROMX_A14 RAM_D11 ROMX_A3 ROMX_A2 RAM_D10 ROMX_A1 RAM_D9 ROMX_A0 RAM_D8 RAM_A0 ROMX_A8 ROMX_A6 RAM_D13 ROMX_A7 RAM_D12 ROMX_A4 RAM_D15 RAM_D14 ROMX_A5 RAM_A10 ROMX_A13 ROMX_A10 RAM_A1 ROMX_A15 RAM_A8 RAM_A7 ROMX_A16 RAM_A2 ROMX_A11 RAM_A3 ROMX_A9 RAM_A5 ROMX_A17 ROMX_A19 SDRAM_BA0 ROMX_D2 RAM_D2 ROMX_D1 RAM_D1 ROMX_D0 RAM_D0 RAM_D4 ROMX_D4 RAM_D5 ROMX_D5 RAM_D3 ROMX_D3 RAM_D6 ROMX_D6 RAM_D7 ROMX_D7 ROMX_CS ROMX_OE ROMX_A2 ROMX_A5 ROMX_A1 ROMX_A4 ROMX_A3 ROMX_A0 ROMX_A6 ROMX_A7 ROMX_A10 ROMX_A13 ROMX_A9 ROMX_A12 ROMX_A11 ROMX_A8 ROMX_A14 ROMX_A15 ROMX_A16 ROMX_A17 ROMX_A19 ROMX_D2 ROMX_D5 ROMX_D1 ROMX_D4 ROMX_D3 ROMX_D0 ROMX_D6 ROMX_D7 RAMX_A10 RAMX_A9 RAMX_A8 RAMX_A7 RAMX_A5 RAMX_A4 RAMX_A3 RAMX_A2 RAMX_A1 RAMX_A0 RAMX_WE RAMX_CAS RAMX_RAS0 SDRAMX_DQM0 SDRAMX_BA0 SDRAMX_CLK SDRAMX_CKE SDRAM_DQM ROMX_OE ROMX_CS ROM_CS RAMX_D15 RAMX_D14 RAMX_D13 RAMX_D12 RAMX_D11 RAMX_D10 RAMX_D9 RAMX_D8 RAMX_D7 RAMX_D6 RAMX_D5 RAMX_D4 RAMX_D3 RAMX_D2 RAMX_D1 RAMX_D0 SDRAM_DQM SDRAM_CKE SDRAM_BA0 SDRAM_BA1 RAM_CLK SDRAM_CAS SDRAM_RAS SDRAM_WE RAM_D1 RAM_D6 RAM_D3 RAM_D13 RAM_D15 RAM_D11 RAM_D5 RAM_D9 RAM_D2 RAM_D0 RAM_D12 RAM_D10 RAM_D14 RAM_D4 RAM_D7 RAM_D8 ROMX_WE SDRAM_BA1 RAMX_A9 RAMX_A8 RAMX_A7 RAMX_A5 RAMX_A4 RAMX_A3 RAMX_A2 RAMX_A1 RAMX_A0 RAMX_RAS0 RAMX_CAS RAMX_WE RAMX_D15 RAMX_D14 RAMX_D13 RAMX_D12 RAMX_D11 RAMX_D10 RAMX_D9 RAMX_D8 RAMX_D7 RAMX_D6 RAMX_D5 RAMX_D4 RAMX_D3 RAMX_D2 RAMX_D1 RAMX_D0 SPIX_DATA0 SPIX_CS SPIX_CLK SPIX_DATA1 SPIX_CLK SDRAM_DQM SPIX_DATA0 SDRAM_CKE ROM_CS SPIX_CS RAMX_A6 RAM_A6 RAMX_A6 RAMX_A6 ROMX_A18 ROMX_A18 RAM_A6 RAM_A9 RAM_A10 RAM_A3 RAM_A1 RAM_A0 RAM_A7 RAM_A8 ROMX_A18 RAM_A4 RAM_A5 RAM_A2 RAM_A6 SPIX_DATA1 SPIX_DATA3 SPIX_DATA2 SDRAM_BA1 RAM_A11 SDRAM_BA0 SPIX_DATA2 SPIX_DATA3 RAM_A11 ROM_CS 1 SDRAM_DQM 1 SDRAM_CKE 1 SDRAM_BA0 1 SDRAM_BA1 1 SDRAM_CLK 1 RAM_D[0..15] 1 RAM_A[0..11] 1 SDRAM_CAS 1 SDRAM_RAS 1 SDRAM_WE 1 RAMVDD3 ROMVDD DGND DGND RAMVDD3 DGND RAMVDD3 DGND DGND DGND RAMVDD3 DGND DGND DGND ROMVDD ROMVDD R67 0 R68 0 BC21 0.1U J4 CON3 1 2 3 U6 SPI_FLASH 1 2 3 4 8 7 6 5 CE DQ0 DQ2 GND VDD DQ3 SCK DQ1 R57 0 U4 256Kx16 EDO DRAM 2 3 4 5 7 8 9 10 31 32 33 34 36 37 38 39 1 6 20 21 35 40 16 17 18 19 22 23 24 25 26 15 14 29 28 13 27 11 12 30 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 VCC VCC VCC GND GND GND A0 A1 A2 A3 A4 A5 A6 A7 A8 A9/NC RAS LCAS UCAS WR OE NC NC NC BC23 0.1U R64 0 BC20 0.1U C31 NC U5 Flash MX29F040/080 12 11 10 9 8 7 6 5 27 26 23 25 4 28 29 3 2 30 31 1 13 14 15 17 18 19 20 21 32 16 22 24 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 D0 D1 D2 D3 D4 D5 D6 D7 VCC GND CE OE R65 0 BC19 0.1U J3 CON3 1 2 3 R72 0 U3 1Mx16 SDRAM 2 3 5 6 8 9 11 12 39 40 42 43 45 46 48 49 32 31 30 29 28 27 24 23 22 21 20 14 15 16 17 18 19 36 35 34 7 13 38 44 1 25 4 10 41 47 50 26 33 37 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 A10/AP LDQM WE CAS RAS CS BA UDQM CLK CKE VDDQ VDDQ VDDQ VDDQ VDD VDD VSSQ VSSQ VSSQ VSSQ VSS VSS NC NC R62 NC/10K 5 4 3 2 1 D D C C B B A A +5V IRI GND STB CLK DAT +5V GND +8V +5V PAD1 PAD0 GND GUN DAT CLK Power On Mute Audio mute PVDD3 Should be set to 3.1~3.3V SPHE8100_DK_2.dsn - 04-Power & UI 1.2 SPHE8100 Release Board Sunplus Technology Co., Ltd. [COMPANY CONFIDENTIAL] B 4 5 Friday, July 22, 2005 Title Size Document Number Rev Date: Sheet of R/L_MUTE R/L_MUTE PAD1 1 PAD0 1 GAME_DAT 1 GAME_CLK 1 GUNIO 1 VFD_CLK 1 IRI 1 VFD_STB 1 VFD_DATA 1 AUD_OUTL 1 AUD_OUTR 1 PGND AVDD3 DVDD3 PVDD3 AVDD3 RFVDD3 RFGND ADVDD3 ADGND DVDD3 DPLVDD3 DPLGND PGND PGND MGND PGND DGND PGND DGND PGND RFGND RFGND DPLGND DGND ADGND DGND VGND DVDD1.8 PGND VCC VCC8 RAMVDD3 DGND VCC DVDD3 VVDD3 DGND DGND SPLVDD3 VCC VCC VCC VCC DGND DGND DGND DGND PGND PGND PGND PGND PGND VCC VCC DGND VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC DGND VCC ADGND DGND ROMVDD DGND VCC DVDD3 BC18 0.1U EC15 47U Q1 8050 + EC3 100U TP5 SHORT TP6 SHORT R26 0 TP1 SHORT R3 180-0805 TP2 SHORT TP7 SHORT Q2 8050 TP4 SHORT R58 NC R80 2K JP1 HEADER 3 1 2 3 BC22 0.1U R5 33-0805 EC4 100U TP3 SHORT BC9 0.1U BC1 0.1U + TC1 10U C43 2200P R76 2K R8 33-0805 BC24 0.1U EC8 10U R48 NC R50 10-0805 C38 2200P L2 Power Bead EC12 10U BC13 0.1U R75 2K R74 10K JP3 HEADER 6 1 2 3 4 5 6 R70 1K J2 Line Out TP 1 2 3 R2 0 R69 1K C41 100P R55 0 R63 4.7K C42 100P Q10 8050 R54 470 L1 Power Bead C36 NC/1000p C37 NC/1000p Q11 8050 BC7 0.1U EC2 220U R53 10K BC4 0.1U R49 7.5K Q9 8550 2 1 3 R19 0 EC16 220u/16V R60 0 R7 390 R6 2K R1 10-0805 R4 10-0805 R43 18 JP4 HEADER 7 1 2 3 4 5 6 7 R61 0 L5 Power Bead D1 3.9V 1 2 EC14 100U 5 4 3 2 1 D D C C B B A A 3 2 6 11 5 7 14 9 Modify note PIC 10 4 15 1 Item 8 12 13 DATE CHANGE LIST: SUNPLUS Inc. 2005/04/06 SPHE8100A Release V1.0 Delete J2,J3,J6,Reset KEY,_RESET1 Pad.connet TX,GAME_CLK,OPCLS,PAD0,PAD1,IRI,GAME_DAT directly.(Page 1) SZ VCD Team 2005/04/08 Change SVIDEO-JACK,RCA JACK to JP4.(Page 2) SZ VCD Team 2005/04/08 Add audio POWER ON mute circut.(page 4) SZ VCD Team 2005/04/08 2005/06/15 2005/06/15 2005/06/15 2005/06/15 rbhung rbhung rbhung rbhung Delete active MIC circuit (R48,R50,EC15,BC7) Delete EC14,EC28,BC23,BC29,EC10,BC17,BC16,EC22,BC11,EC6,L2,BC18, BC32,BC33,L16,EC25,EC13 FOR Cost-down Marge DAVDD3 to ADVDD3 Modify L3=>R78,L5=>R81,L9=>R79,L10=>R83,L11=>R82,L15=>R80 Modify EC1 from 220U=>100U, EC23 from 100U=>47U rbhung 2005/06/15 Modify R33 from 5.1K=>3K, C10 from 0.22U=>0.15U rbhung 2005/06/15 Modify SPI FLASH Interface & Add H/W config option rbhung 2005/06/15 Modify SPI FLASH DATA3 net to SPHE8100 Pin15 rbhung 2005/07/15 SPHE8100_DK_2.dsn - 05-Change List 1.2 SPHE8100 DK Board Sunplus Technology Co., Ltd. [COMPANY CONFIDENTIAL] B 5 5 Friday, July 22, 2005 Title Size Document Number Rev Date: Sheet of

版权声明

1. 本站所有素材,仅限学习交流,仅展示部分内容,如需查看完整内容,请下载原文件。

2. 会员在本站下载的所有素材,只拥有使用权,著作权归原作者所有。

3. 所有素材,未经合法授权,请勿用于商业用途,会员不得以任何形式发布、传播、复制、转售该素材,否则一律封号处理。

4. 如果素材损害你的权益请联系客服QQ:77594475 处理。