CXD3068+CL8830A原理图

)

)

)

)

)

)

)

)

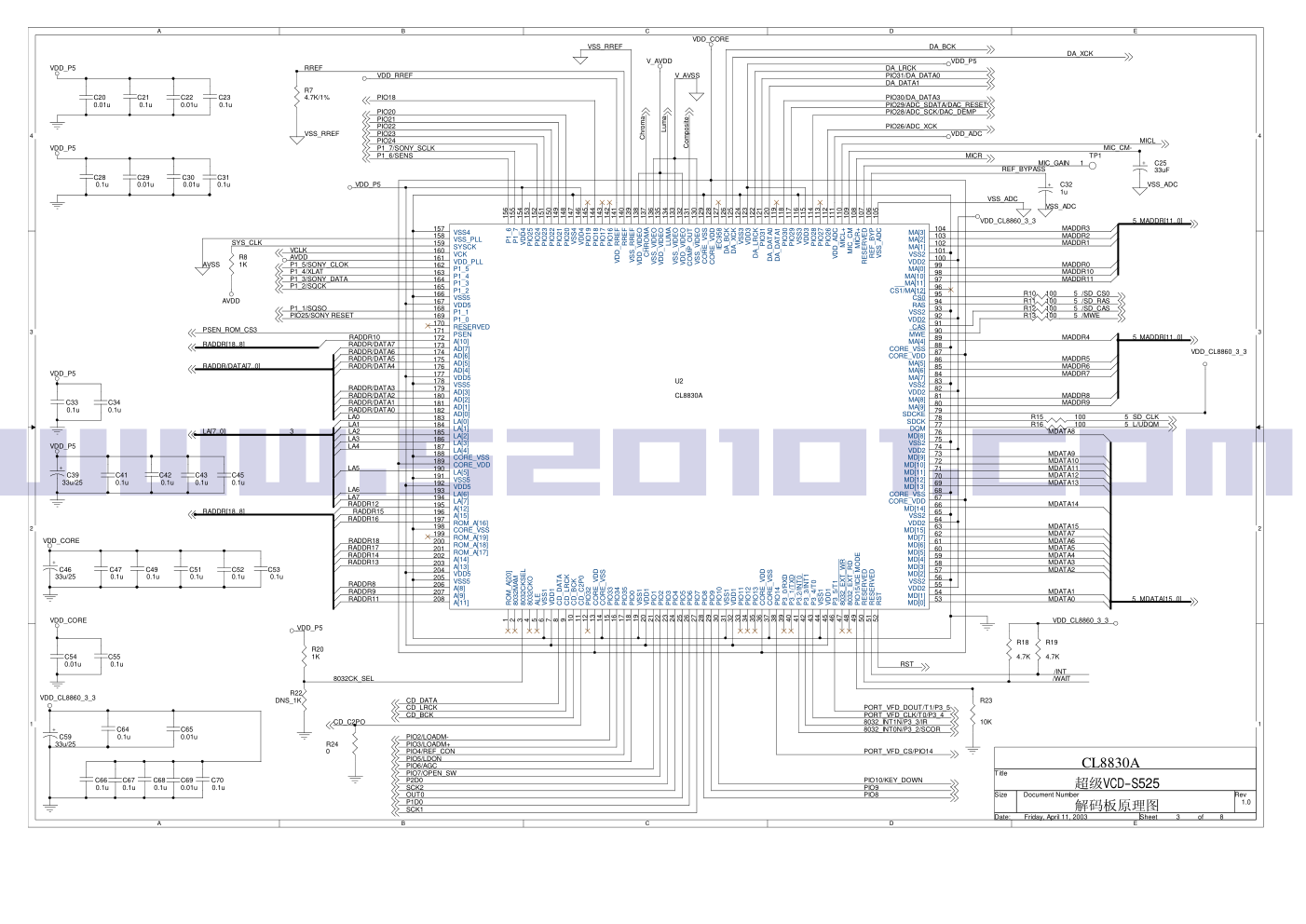

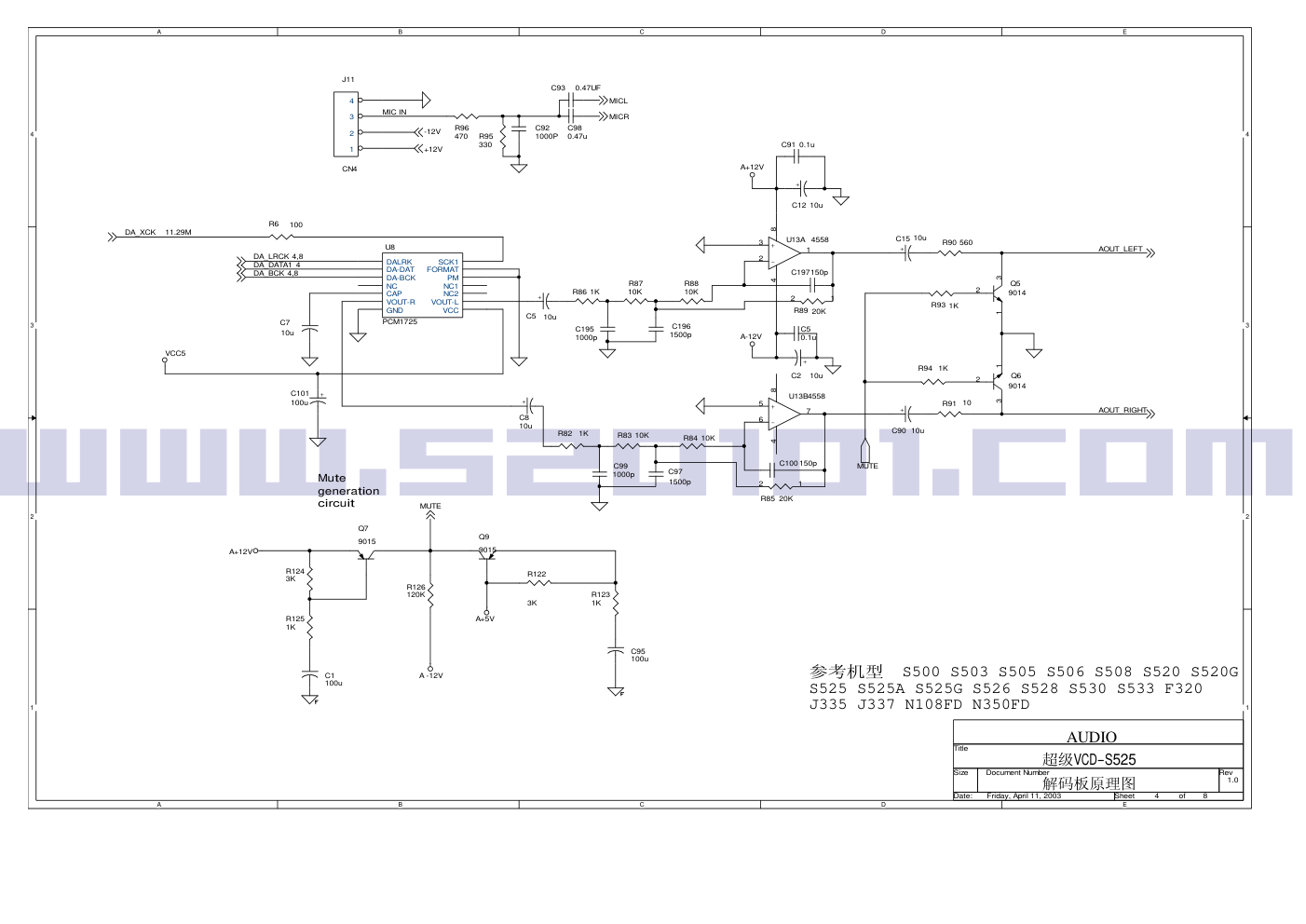

www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 VFD Stuffing Options CONNECTORS 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 1 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of Chroma Composite CVBSVIDEO Luma YVIDEO CVIDEO PORT_VFD_CLK/T0/P3_4 3 PORT_VFD_DOUT/T1/P3_5 3 8032_INT1N/P3_3/IR 3 PORT_VFD_CS/PIO14 3 VCLK 4,6 V_AVDD VCC5 VCC5 VCC5 V_AVSS V_AVSS V_AVSS V_AVSS C183 100P C184 100P C185 100P R2 75/1% R3 75/1% R1 75/1% CN1 PH6A 6 1 2 3 4 5 D1 DIN4148 1 2 D2 DIN4148 1 2 R77 100 R78 100 R79 100 C16 0.1u C186 100P Y1 27MHz-F C13 270p C14 270p R5 3.3K C17 20P L5 FER_HI_IMP C18 20P R80 100 U1A 74HCU04 1 2 14 7 U1B 74HCU04 3 4 14 7 R4 100 www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 23 P2D0 24 SCK2 26 P1D0 27 SCK1 P2D0 GND RESET SCK2 +5V GND RESET P1D0 SCK1 +5V RESET 25 P2D0 SCK2 P1D0 +5V RESET SCK1 GND 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 2 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of CL8830AV PIO4 CL8830AV PIO5 CL8830AV PIO6 CL8830AV PIO7 CL8830AV PIO3 J12 CON5 1 2 3 4 5 6 7 J13 CON6 1 2 3 4 5 6 7 8 9 J14 CON7 1 2 3 4 5 6 7 8 9 www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 CL8830A 解码板原理图 1.0 超级VCD-S525 3 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of RADDR/DATA7 RADDR15 MDATA13 MDATA9 MADDR4 MADDR1 8032CK_SEL MADDR6 MADDR2 RADDR/DATA3 RADDR/DATA0 LA3 RADDR16 MDATA12 MDATA5 RADDR/DATA5 RADDR8 MDATA2 MDATA7 MADDR0 LA4 MDATA3 MADDR9 /WAIT MIC_GAIN SYS_CLK RADDR/DATA4 LA0 LA2 MDATA15 LA1 MDATA0 MDATA10 MADDR3 LA7 RADDR14 MDATA8 RREF REF_BYPASS RADDR10 RADDR17 MDATA1 MIC_CM- LA5 LA6 MDATA4 /INT RADDR/DATA2 RADDR/DATA1 RADDR18 MDATA14 MADDR11 MDATA6 RADDR12 RADDR11 MDATA11 RADDR9 MADDR5 RADDR/DATA6 RADDR13 MADDR8 MADDR10 MADDR7 /SD_CS0 5 /MWE 5 /SD_RAS 5 /SD_CAS 5 L/UDQM 5 SD_CLK 5 PIO20 CD_BCK Composite PIO6/AGC PIO22 Chroma CD_DATA DA_XCK P1_4/XLAT DA_DATA1 PIO4/REF_CON PIO24 PORT_VFD_DOUT/T1/P3_5 PIO29/ADC_SDATA/DAC_RESET MICL PIO2/LOADM- MICR PORT_VFD_CS/PIO14 PIO8 P1_2/SQCK CD_C2PO 8032_INT0N/P3_2/SCOR P1_6/SENS PIO10/KEY_DOWN MADDR[11..0] 5 MADDR[11..0] 5 PIO18 LA[7..0] 3 PIO5/LDON PSEN_ROM_CS3 RST Luma DA_BCK CD_LRCK P1_5/SONY_CLOK RADDR/DATA[7..0] PIO21 PIO23 PIO30/DA_DATA3 PIO25/SONY RESET DA_LRCK P1_3/SONY_DATA PIO31/DA_DATA0 PIO28/ADC_SCK/DAC_DEMP RADDR[18..8] PIO7/OPEN_SW PIO3/LOADM+ PORT_VFD_CLK/T0/P3_4 MDATA[15..0] 5 PIO9 P1_1/SQSO PIO26/ADC_XCK RADDR[18..8] 8032_INT1N/P3_3/IR VCLK P1_7/SONY_SCLK P2D0 SCK2 OUT0 P1D0 SCK1 AVDD VDD_CL8860_3_3 VDD_P5 VDD_P5 VDD_RREF VDD_CORE VDD_P5 VDD_CL8860_3_3 VDD_CORE VDD_P5 VDD_P5 VDD_P5 AVDD VDD_ADC VDD_CORE V_AVDD VDD_P5 VDD_CL8860_3_3 VDD_CL8860_3_3 VSS_RREF VSS_ADC VSS_ADC V_AVSS VSS_RREF AVSS VSS_ADC + C59 33u/25 C45 0.1u C64 0.1u C42 0.1u C66 0.1u C43 0.1u C68 0.1u + C39 33u/25 C70 0.1u R18 4.7K C41 0.1u R19 4.7K R23 10K C51 0.1u R7 4.7K/1% + C46 33u/25 + C32 1u C53 0.1u R8 1K R22 DNS_1K R24 0 C52 0.1u C67 0.1u C54 0.01u C55 0.1u C65 0.01u R20 1K C69 0.01u C49 0.1u C21 0.1u C47 0.1u R16 100 C23 0.1u R13 100 C20 0.01u R12 100 R11 100 C22 0.01u R10 100 C30 0.01u C29 0.01u TP1 1 C28 0.1u U2 CL8830A 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 VSS4 VSS_PLL SYSCK VCK VDD_PLL P1_5 P1_4 P1_3 P1_2 VSS5 VDD5 P1_1 P1_0 RESERVED PSEN A[10] AD[7] AD[6] AD[5] AD[4] VDD5 VSS5 AD[3] AD[2] AD[1] AD[0] LA[0] LA[1] LA[2] LA[3] LA[4] CORE_VSS CORE_VDD LA[5] VSS5 VDD5 LA[6] LA[7] A[12] A[15] ROM_A[16] CORE_VSS ROM_A[19] ROM_A[18] ROM_A[17] A[14] A[13] VDD5 VSS5 A[8] A[9] A[11] MD[0] MD[1] VDD2 VSS2 MD[2] MD[3] MD[4] MD[5] MD[6] MD[7] MD[15] VDD2 VSS2 MD[14] CORE_VDD CORE_VSS MD[13] MD[12] MD[11] MD[10] MD[9] VDD2 VSS2 MD[8] DQM SDCK SDCKE MA[9] MA[8] VDD2 VSS2 MA[7] MA[6] MA[5] CORE_VDD CORE_VSS MA[4] MWE CAS VDD2 VSS2 RAS CS0 CS1/MA[12] MA[11] MA[10] MA[0] VDD2 VSS2 MA[1] MA[2] MA[3] ROM_A[20] 8032MAM 8032CKSEL 8032CKO ALE VSS1 VDD1 CD_DATA CD_LRCK CD_BCK CD_C2P0 PIO32 CORE_VDD CORE_VSS PIO33 PIO34 PIO35 PIO0 VSS1 VDD1 PIO1 PIO2 PIO3 PIO4 PIO5 PIO6 PIO7 PIO8 PIO9 PIO10 VSS1 VDD1 PIO11 PIO12 PIO13 CORE_VDD CORE_VSS PIO14 P3_0/RXD P3_1/TXD P3.2/INT0 P3_3/INT1 P3_4/T0 VSS1 VDD1 P3_5/T1 8032_EXT_WR 8032_EXT_RD PIO15/ICE MODE RESERVED RESERVED RST VSS_ADC REF_BYP RESERVED MICR+ MIC_CM MICL+ VDD_ADC PIO26 PIO27 PIO28 VDD3 VSS3 PIO29 PIO30 DA_DATA1 DA_DATA0 PIO31 DA_LRCK VDD3 VSS3 DA_XCK DA_BCK IEC958 CORE_VDD CORE_VSS VSS_VIDEO COMP_OUT VDD_VIDEO VSS_VIDEO LUMA VDD_VIDEO VSS_VIDEO CHROMA VDD_VIDEO VSS_RREF RREF VDD_RREF PIO16 PIO17 PIO18 PIO19 VDD4 VSS4 PIO20 PIO21 PIO22 PIO23 PIO24 PIO25 VDD4 P1_7 P1_6 C31 0.1u C34 0.1u C33 0.1u + C25 33uF R15 100 www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 Mute generation circuit AUDIO 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 4 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of MIC IN AOUT_LEFT DA_XCK 11.29M AOUT_RIGHT DA_BCK 4,8 DA_DATA1 4 DA_LRCK 4,8 +12V -12V MICR MICL MUTE A+12V VCC5 A-12V A+12V A -12V A+5V C95 100u C1 100u R83 10K C196 1500p C97 1500p + C8 10u + C12 10u R88 10K C195 1000p + - U13B4558 5 6 7 8 4 C100 150p C7 10u R86 1K R82 1K J11 CN4 1 2 3 4 + - U13A 4558 3 2 1 8 4 C92 1000P R87 10K R95 330 C91 0.1u R6 100 R96 470 C5 0.1u C98 0.47u R84 10K C93 0.47UF Q5 9014 2 1 3 + C101 100u C99 1000p Q6 9014 2 1 3 + C2 10u R91 10 R90 560 + C15 10u + C90 10u U8 PCM1725 DALRK DA-DAT DA-BCK NC CAP VOUT-R GND VCC VOUT-L NC2 NC1 PM FORMAT SCK1 R93 1K R125 1K R94 1K R126 120K R123 1K R122 3K Q9 9015 C197150p R89 20K 1 2 R85 20K 1 2 R124 3K Q7 9015 + C5 10u MUTE www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 Reset circuit TO-92 package bottom view E B C + 5V Power from Connector + 5V Power to 8860 PLL Decoupling Capacitor Video DAC Decoupling Capacitor ADC Decoupling Capacitor During Layout, try to place 2 .1/A capacitors + 3V Power to CL8860 PLL + 3V Power to CL8860 Video DAC + 3V Power to SDRAM + 3V Power to Digital CL8860 + 3V Power to CL8860 RREF CVD3 CORE(350ma) POWER 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 5 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of VSS_RREF RST 3 /HARD_RESET VCC5 VCC5 VDD_P5 VDD_RREF V_AVDD AVDD VDD_ADC V_AVDD AVDD VCC3 SDRAM_PWR VDD5 VDD_RREF VDD_CL8860_3_3 VCC5 +5VS VDD_CORE VCC3 AVSS VSS_ADC V_AVSS L10 FER_HI_IMP + C205 100u/25 L2 FER_HI_IMP + C117 33u/25 D14 1N4148 1 2 L13 FER_HI_IMP R143 220 U11 BD140 2 1 3 C118 10u/25 Q14 8050 2 1 3 D9 1N4148 1 2 Z1 3v3 R142 330 Q2 8550 2 1 3 R34 1K R32 10K R33 1K C108 0.1u C111 0.1u C107 0.1u C110 0.1u + C206 100u/25 C109 0.1u C114 0.1u C112 0.01u C115 0.01u C106 0.01u C125 0.33U + C105 33u/25 + C113 33u/25 L12 FER_HI_IMP D7 D1N4001 1 2 + C116 33u/25 + C124 33u/25 + C121 33u/25 L9 FER_HI_IMP L14 FER_HI_IMP C119 0.1u C120 0.1u L19 FER_HI_IMP www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 SONY_DGND is connected to digital ground though copper dot SONY_AGND is connected to digital ground though copper dot SONY DSP 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 6 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of SONY_RESET P1_6/SENS P1_5/SONY_CLOK RF VC TE FE SLIM FCS+ P1_2/SQCK CD_C2PO CD_DATA SLED- MDP 8032_INT0N/P3_2/SCOR P1_4/XLAT P1_7/SONY_SCLK TRK- FCS- CD_BCK P1_1/SQSO CD_LRCK TRK+ SLED+ P1_3/SONY_DATA PIO25/SONY_RESET /HARD_RESET +5VS +5VS VCC_SONY_D VCC_SONY_A VCC_SONY_D VCC_SONY_D VCC_SONY_A VCC_SONY_D SONY_AGND SONY_AGND SONY_AGND C134 0.47u C137 100p C136 1000P C148 22p C147 22p Y2 16.9344Mhz C135 0.01u R38 1K C102 0.1u R40 820K R51 4.7K R52 4.7K R39 180K R41 33K C138 470p R43 470K C127 1500p R36 100K D10 1N4148 1 2 R49 6.8K R138 1.8K U6 CXD3068Q 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 DVDD0 XRST MUTE DATA XLAT CLOK SENS SCLK ATSK WFCK XUGF XPCK GFS C2PO SCOR C4M WDCK DVSS0 COUT MIRR SE FE VC TES1 TEST DVSS1 FRDR FFDR TRDR TFDR SRDR SFDR DVDD1 FSTO SSTP MDP LOCK PWMI FOK DFCT VPCO V16M VCTL BIAS AVDD1 PCO FILI FILO CLTV AVSS1 RFAC ASYI YASYO AVDD0 IGEN AVSS0 ADIO RFDC CE TE DVDD2 ASYE MD2 DOUT LRCK PCMD BCK EMPH XTSL DVSS2 XTAI XTAO SOUT SOCK XOLT SQSO SQCK SCSY SBSO EXCK + C141 33u/25 C129 0.1u C131 0.1u C132 0.1u C140 0.1u C143 0.1u D11 1N4148 1 2 C145 0.1u C139 0.1u + C128 220u/16 + C130 100u/16 R47 100 L16 FER_HI_IMP L15 FER_HI_IMP R54 DNS_100 C142 0.1u R48 100 R44 15K R45 100K R46 15K R139 3.3K R42 1M C133 0.1u R35 10K R37 10K R50 10K R53 4.7K C146 470p C144 470p www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 RF AND MOTOR AMP 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 7 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of E PD F SP+ SP- T- T+ LIM SONY-AGND GND VR AVCC A B C D F+ F- SL- SL+ LD VC OPEN/CLOSE REV (LMR) FWD (LMF) VC_3068 P1025/SONY-RESET FE_3068 SLED- SLED+ FCS+ FCS- LIM MDP TE_3068 LD-ON AGCCONT SLED- SLED+ TRK+ TRK- TRK+ TRK- RF-3068 P104/REF 3.3V 3.3v SVCC MGND SVCC +8V MGND MGND MGND ANGND AVDD GND1 +5v 3v3 R69 150 R67 2K C204 220U C141 47U R133 3K C?? 0.1U R66 150K R59 4.7 R100 560 C165 150P C151 0.33U C152 0.1U C200 47U JP2 GREEN (2mm) 1 2 3 4 5 6 BA6208 U12 1 2 3 4 5 6 7 8 9 NC BIN AIN NC GND VCC BOUT AOUT NC CN2 BLACK (2mm) 1 2 3 4 5 U8 BA6392FP 28 21 27 1 26 20 25 24 2 23 19 22 3 18 4 17 16 15 5 6 7 8 9 10 11 12 13 14 29 30 GND3 VCC1 OUT4F OUT1F OUT4R FIN3 VBIN1 VSIN OUT1R VBIN RIN3 VCC2 RCIN1 RCIN3 RIN1 OUT3R OUT3F MUTE FIN1 VREFIN VREOUT GND1 FIN2 RIN2 RCIN2 OUT2R OUT2F GND2 GND4 GND5 R60 10K R135 3.3K R61 10K C156 22N C155 0.1U R55 10K + C178 100U R65 10 R71 10K L6 10UH C140 0.1U C160 0.068U C169 100U/16V C161 0.1U Q8 8550C 3 1 2 C150 1000P R73 3.3K R101 560 R102 180 C178 0.1U R127 56K L20 10UH D13 2v7 Q11 8050c R147 10k R137 47k Q10 8050c R134 47k C14910U/25V R103 1.8k R136 3.3K R130 56K R128 56K Q4 8050c R129 56K JP1 CON16 (2mm) 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 R57 110k R58 110k R72 1M R70 1K R132 open C153 100U C158 100U C163 100U C159 1U CXA2550N 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 AGCVTH LD PD PD1 PD2 VEE F E EI VC TE FE_BIAS FE RFM RFO RFI RFTC AGCCONT LD_ON VCC R74 3.3K C177 0.1U R56 1K R131 open R68 10K C157 0.01U C171 47U C164 47P www.520101.co A A B B C C D D E E 4 4 3 3 2 2 1 1 ROM NAME AT29C020 AT29C040 AT27C020 AT27C040 SIZE 256KX8 512KX8 256KX8 512KX8 TYPE FLASH FLASH ROM ROM R25 R26 R27 R28 X X X X X X X 参考机型 S500 S503 S505 S506 S508 S520 S520G S525 S525A S525G S526 S528 S530 S533 F320 J335 J337 N108FD N350FD 解码板原理图 1.0 超级VCD-S525 8 8 Friday, April 11, 2003 Title Size Document Number Rev Date: Sheet of MDATA0 MDATA1 MDATA2 MDATA3 MDATA4 MDATA5 MDATA6 MDATA7 MDATA14 MDATA13 MDATA12 MDATA11 MDATA10 MDATA9 MDATA8 MADDR11 MADDR10 MADDR0 MADDR1 MADDR2 MADDR3 MADDR5 MADDR6 MADDR7 MADDR8 MADDR9 L/UDQM SDRAM_PWR MDATA15 MADDR4 LA0 LA1 LA2 LA3 LA4 LA5 LA6 LA7 RADDR/DATA0 RADDR/DATA1 RADDR/DATA2 RADDR/DATA5 RADDR/DATA6 RADDR/DATA7 RADDR/DATA4 RADDR/DATA3 RADDR10 RADDR13 RADDR15 RADDR14 RADDR9 RADDR16 RADDR12 RADDR18 RADDR17 RADDR8 RADDR11 /SD_RAS 4 /SD_CAS 4 /SD_CS0 4 L/UDQM 4 /MWE 4 SD_CLK 4 MADDR[11..0] 4 MDATA[15..0] 4 LA[7..0] RADDR/DATA[7..0] PSEN_ROM_CS RADDR[18..8] SDRAM_PWR SDRAM_PWR VDD_P5 VDD_P5 VDD_P5 VDD_P5 SDRAM_PWR R28 DNS-0 C72 0.1u C79 0.01u + C74 33u/25 C73 0.01u C81 0.01u C76 0.1u C82 0.1u + C75 33u/25 C78 0.1u C80 0.1u U3 SDRAM_1Mx16 2 3 5 6 8 9 11 12 39 40 42 43 45 46 48 49 21 22 23 24 27 28 29 30 31 32 20 14 15 16 17 18 19 34 35 36 33 37 1 7 13 25 38 44 4 10 26 41 47 50 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 DQML WE CAS RAS CS BA CKE CLK DQMU NC NC VCC VCC VCC VCC VCC VCC GND GND GND GND GND GND C77 0.01u U4 AT49F020-32DIP 12 11 10 9 8 7 6 5 27 26 23 25 4 28 29 3 2 22 24 31 1 13 14 15 17 18 19 20 21 32 16 30 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 CE OE PGM VPP D0 D1 D2 D3 D4 D5 D6 D7 VCC GND A17 R25 4.7K R27 DNS-0 R26 4.7K

版权声明

1. 本站所有素材,仅限学习交流,仅展示部分内容,如需查看完整内容,请下载原文件。

2. 会员在本站下载的所有素材,只拥有使用权,著作权归原作者所有。

3. 所有素材,未经合法授权,请勿用于商业用途,会员不得以任何形式发布、传播、复制、转售该素材,否则一律封号处理。

4. 如果素材损害你的权益请联系客服QQ:77594475 处理。